中科院基于新型SiC复合衬底的低成本MOSFET取得重要进展

时间:2025-01-17 08:28:10 440浏览 收藏

本篇文章给大家分享《中科院基于新型SiC复合衬底的低成本MOSFET取得重要进展》,覆盖了科技周边的常见基础知识,其实一个语言的全部知识点一篇文章是不可能说完的,但希望通过这些问题,让读者对自己的掌握程度有一定的认识(B 数),从而弥补自己的不足,更好的掌握它。

中科院微电子所刘新宇研究员团队与合作伙伴成功研制出高性能低成本1200V SiC MOSFET,该成果基于新型6英寸SiC复合衬底。

SiC晶圆产业面临产能扩张与高质量衬底成品率低的挑战(40%-60%)。大量低质量衬底被浪费,导致成本居高不下(通常超过MOSFET总成本的50%),并造成高碳排放。

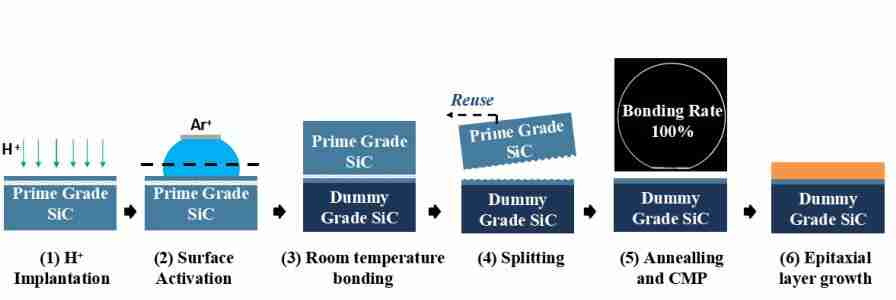

该团队创新性地提出并实现了6英寸单晶SiC复合衬底,利用表面活化键合和离子注入剥离技术,将高质量SiC薄层转移到低质量衬底上,实现低质量衬底的有效利用。每个高质量SiC晶圆可重复使用超过30次,预计成本降低40%。

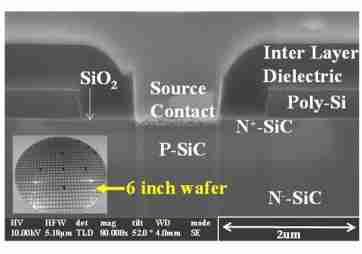

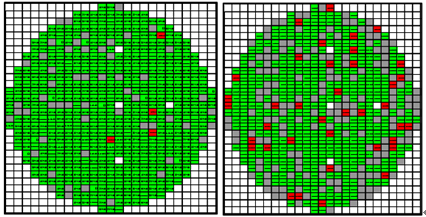

该复合衬底缺陷密度低,界面热阻低至2.8 +1.4/-0.7 m²K/GW(国际最低值),且键合界面电场强度小。基于该衬底制造的6英寸SiC外延层,无致命缺陷良率高达99.2%。最终制成的1200V、20mΩ SiC MOSFET器件良率超过70%。

相关研究成果已于12月10日在第70届国际电子器件大会(IEDM 2024)上以口头报告形式发表。

图1. 6英寸SiC-SiC键合制造工艺流程图

图2. 6英寸工程衬底和外延层上SiC MOSFET沟道区域高分辨率透射电镜(HRTEM)图像

图3. VGS= -4V,VDS=1200V条件下,6英寸晶圆上器件IGSS分布图 (图a良率90%,图b良率70%)

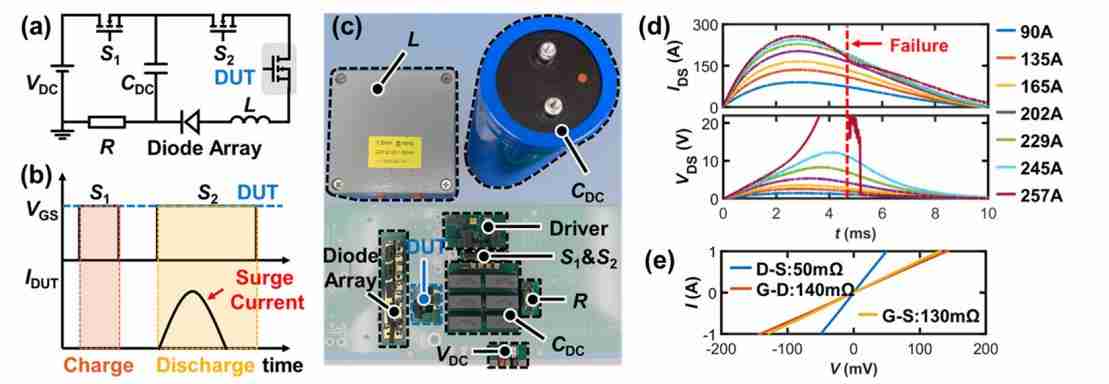

图4. 浪涌电路测试结果:(a)电路原理图;(b)理想波形;(c)浪涌电流测试装置照片;(d)不同浪涌电流水平下器件电流电压波形;(e)失效器件引脚间电阻。

文章来源:中国科学院微电子研究所

理论要掌握,实操不能落!以上关于《中科院基于新型SiC复合衬底的低成本MOSFET取得重要进展》的详细介绍,大家都掌握了吧!如果想要继续提升自己的能力,那么就来关注golang学习网公众号吧!

-

501 收藏

-

501 收藏

-

501 收藏

-

501 收藏

-

501 收藏

-

204 收藏

-

411 收藏

-

411 收藏

-

331 收藏

-

140 收藏

-

380 收藏

-

229 收藏

-

190 收藏

-

485 收藏

-

353 收藏

-

473 收藏

-

418 收藏

-

- 前端进阶之JavaScript设计模式

- 设计模式是开发人员在软件开发过程中面临一般问题时的解决方案,代表了最佳的实践。本课程的主打内容包括JS常见设计模式以及具体应用场景,打造一站式知识长龙服务,适合有JS基础的同学学习。

- 立即学习 543次学习

-

- GO语言核心编程课程

- 本课程采用真实案例,全面具体可落地,从理论到实践,一步一步将GO核心编程技术、编程思想、底层实现融会贯通,使学习者贴近时代脉搏,做IT互联网时代的弄潮儿。

- 立即学习 516次学习

-

- 简单聊聊mysql8与网络通信

- 如有问题加微信:Le-studyg;在课程中,我们将首先介绍MySQL8的新特性,包括性能优化、安全增强、新数据类型等,帮助学生快速熟悉MySQL8的最新功能。接着,我们将深入解析MySQL的网络通信机制,包括协议、连接管理、数据传输等,让

- 立即学习 500次学习

-

- JavaScript正则表达式基础与实战

- 在任何一门编程语言中,正则表达式,都是一项重要的知识,它提供了高效的字符串匹配与捕获机制,可以极大的简化程序设计。

- 立即学习 487次学习

-

- 从零制作响应式网站—Grid布局

- 本系列教程将展示从零制作一个假想的网络科技公司官网,分为导航,轮播,关于我们,成功案例,服务流程,团队介绍,数据部分,公司动态,底部信息等内容区块。网站整体采用CSSGrid布局,支持响应式,有流畅过渡和展现动画。

- 立即学习 485次学习