伪栅去除技术详解

时间:2025-03-01 21:36:38 233浏览 收藏

本文探讨集成电路制造中至关重要的伪栅去除技术,重点分析了高介电常数金属栅极(HKMG)工艺下,先栅极和后栅极工艺的差异及伪栅去除工艺的细节。文章详细介绍了湿法、干法结合湿法以及纯干法三种伪栅去除工艺的原理、优缺点及应用,并深入分析了键能差异、电子温度、蚀刻气体选择等关键因素对蚀刻效率和器件可靠性的影响,尤其关注了同步脉冲等离子体工艺在提高纯干法蚀刻效率和选择比方面的作用,为提升集成电路性能提供技术参考。 关键词:伪栅去除,高k金属栅极,HKMG,干法蚀刻,湿法蚀刻,同步脉冲等离子体,集成电路制造

本文探讨了集成电路制造中关键的伪栅去除技术,并对比分析了高介电常数栅极工艺、先栅极工艺和后栅极工艺。文章重点阐述了伪栅去除工艺的细节。

高介电常数金属栅极工艺

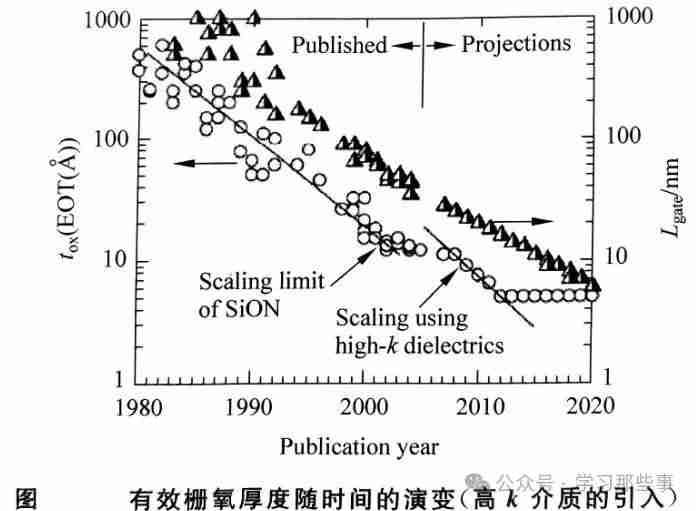

随着CMOS集成电路特征尺寸不断缩小,等效栅氧化层厚度成为制约晶体管性能的关键。然而,栅氧化层厚度减小受限于隧穿漏电效应,当氧化硅层薄于2nm时,隧穿漏电显著增加,甚至呈指数级增长,使得1nm以下的栅氧化层厚度难以实现。

为解决这一问题,英特尔公司率先在45nm节点引入高k技术,其他厂商随后在32nm或28nm节点跟进。

高介电常数栅介电层(HK)与金属栅极(MG)技术结合成为当前逻辑电路的主流。虽然两者并非必然关联,但高k栅介电层带来的高电场强度要求栅极材料具备更优的导电性和稳定性,因此金属栅极成为理想选择。金属栅极可有效降低栅极耗尽效应,提升晶体管性能。

先栅极工艺与后栅极工艺对比

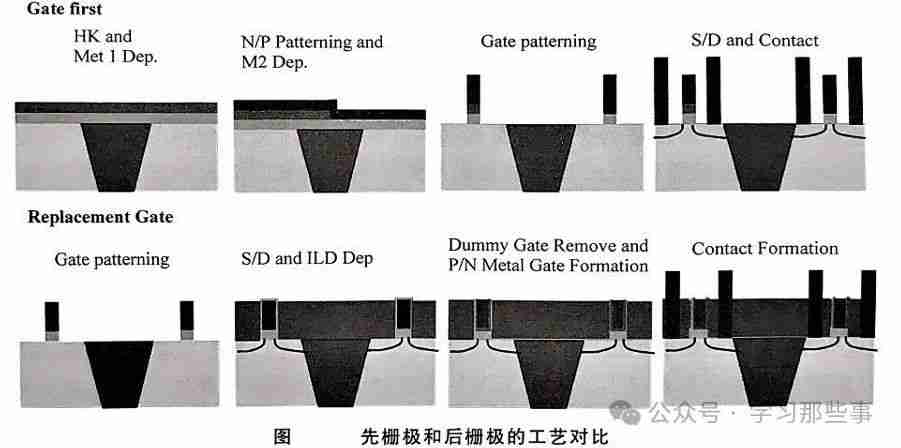

CMOS集成电路制造中,“硅栅自对准”工艺占据主导地位。此工艺先形成栅介电层和栅极(通常为多晶硅),再进行源极和漏极离子掺杂。栅极结构阻挡作用使得离子掺杂自动与硅栅对准,后续高温退火激活掺杂离子。

然而,金属栅极在“硅栅自对准”工艺中面临诸多挑战,例如阈值电压变化等。为克服这些问题,业界采用多晶硅伪栅技术。

在离子掺杂和退火等关键步骤完成后,通过化学气相沉积填充氧化硅膜,并采用化学机械抛光平坦化,使伪栅显露出来。然后去除多晶硅伪栅,使用功函数金属和栅极金属填充形成金属栅。此过程即为后栅极工艺。

后栅极工艺增加了伪栅去除和金属填充等步骤,对伪栅去除工艺要求很高,需在不损伤沟道的情况下完全去除伪栅材料。金属填充则面临高深宽比挑战,需要先进的填充技术和材料以确保金属栅的完整性和可靠性。

尽管后栅极工艺成本高且工艺复杂,但长期以来被认为是实现高介电常数栅介电层与金属栅极(HKMG)结合的必要方案。然而,随着技术进步,部分公司(如IBM)正在研发无需后栅极工艺的替代方案。例如,通过特定介电材料(如硅酸铪)和栅极材料匹配,可在高温下保持热力学稳定性,简化工艺流程并降低成本。

此外,先栅极工艺也在不断发展。虽然先栅极工艺中的“金属栅”实际上只是在栅介电层上增加一层高熔点金属,但仍需多晶硅栅极来实现“硅栅自对准”的其他工序。随着材料科学和工艺技术的进步,未来可能出现更多创新方案,进一步简化CMOS集成电路制造工艺并提升性能。

伪栅去除工艺详解

CMOS集成电路后栅极工艺中,伪栅去除至关重要。目前,业界主要采用三种伪栅去除工艺:湿法蚀刻、干法结合湿法蚀刻以及纯干法蚀刻。

-

湿法蚀刻工艺: 通常使用四甲基氢氧化铵等化学溶液去除多晶硅伪栅。此方法避免了干法蚀刻可能造成的等离子体损伤。然而,由于离子注入过程中部分掺杂离子不可避免地进入伪栅上半部分,导致湿法蚀刻速率对掺杂多晶硅非常敏感。尤其当伪栅掺杂硼元素时,四甲基氢氧化铵蚀刻速率显著降低,限制了湿法蚀刻的单独应用。

-

干法结合湿法蚀刻工艺: 为克服湿法和干法蚀刻各自局限性,业界开发了干法结合湿法蚀刻工艺。此工艺先使用干法蚀刻去除伪栅上部的掺杂多晶硅层,减少湿法蚀刻的敏感性和不均匀性。然后,采用湿法蚀刻去除剩余未掺杂多晶硅。此方法结合了干法和湿法的优点,既避免了等离子体损伤,又提高了蚀刻的均匀性和可控性。然而,由于湿法蚀刻的各向同性特性,此方法通常只适用于同时去除N型和P型伪栅。后续功函数金属填充工艺中,仍需重新定义图形并去除不需要的功函数金属,因此整体工艺流程并未显著简化。

-

纯干法蚀刻工艺: 纯干法蚀刻工艺是一种更先进、灵活的伪栅去除方法。此工艺先去除伪栅表面覆盖的原生氧化硅层,通常采用碳氟气体蚀刻。在去除原生氧化硅的同时,尽量减少蚀刻表面副产物的残留。接下来的伪栅主蚀刻步骤则采用HBr与O2混合气体,在电感耦合等离子体反应腔体中进行。硅与溴反应形成弱挥发性的溴化硅副产物,从而实现较高的多晶硅对氧化硅的选择比。在去除伪栅多晶硅的同时,蚀刻会停止在高介电常数栅氧化层的保护层上,且对层间介质层的损伤较小。

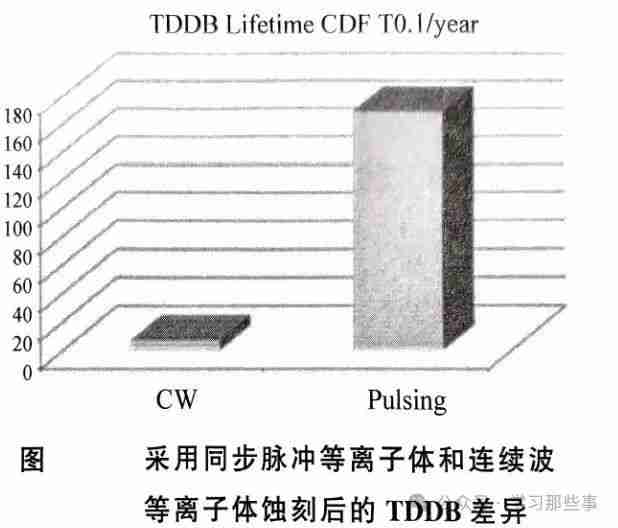

为进一步提高纯干法蚀刻的效率和可控性,业界引入了同步脉冲等离子体工艺。此工艺通过控制等离子体的开关时间和占空比,降低等离子体电子温度,从而减轻高能粒子注入沟道区带来的风险。同步脉冲等离子体蚀刻能够减少HBr的过度解离,降低等离子体氢离子浓度,进而减少被电场加速注入沟道的氢离子数量。这不仅提高了伪栅去除的均匀性和可控性,还有效改善了NBTI(负偏置温度不稳定性)等可靠性问题。

在伪栅去除工艺中,物理性能的考量对于确保工艺高效性和器件可靠性至关重要。键能差异和电子温度对蚀刻过程有显著影响。

-

键能差异与蚀刻选择比: 由于Si-O键键能(460kJ/mol-1)远高于Si-Si键键能(176kJ/mol-1),导致蚀刻过程中,氧化硅层相对于多晶硅层具有更高的稳定性。极低的电子温度,例如同步脉冲伪栅去除蚀刻工艺提供的,能够显著降低对氧化硅层间介电层的蚀刻速率。这种降低的蚀刻速率使得伪栅和层间介电层之间的蚀刻选择比上升,有助于在去除伪栅的同时保护层间介电层不受损伤。

-

层间介电层消耗与金属栅高度: 同步脉冲蚀刻工艺的优势在于,它能够在蚀刻过程中显著减少层间介电层的消耗。通过优化蚀刻条件,层间介电层的消耗从50Å减少到20Å。这种减少的消耗将明显提高金属栅的高度,进而降低金属栅的电阻。这对于提高器件的性能和可靠性至关重要。

-

蚀刻气体的选择: 蚀刻气体的选择也是关键因素。传统的HBr气体与多晶硅栅反应时,会形成难以挥发的副产物,增加了去除难度。为达到去除目的,通常需要增加偏置功率,但这可能导致离子轰击增强,对器件造成损伤。为克服这一问题,业界开始探索使用氢气作为蚀刻气体。氢气分子在源功率的作用下解离为氢原子,这些氢原子与硅反应形成硅烷(SiH₄)。硅烷具有较低的沸点,因此其气化性远大于溴化硅(SiBr₄)。这意味着在蚀刻过程中,硅烷副产物更容易被去除,无需使用偏置功率即可达到清洁的蚀刻表面。实验证明,采用无偏置功率氢气等离子体的伪栅去除工艺对伪栅底部的高k材料保护层具有更高的选择比和更少的损伤。从器件性能角度看,这种工艺能够大幅降低金属栅极漏电,相比其他工艺可降低50%。

到这里,我们也就讲完了《伪栅去除技术详解》的内容了。个人认为,基础知识的学习和巩固,是为了更好的将其运用到项目中,欢迎关注golang学习网公众号,带你了解更多关于蚀刻气体的知识点!

-

501 收藏

-

501 收藏

-

501 收藏

-

501 收藏

-

501 收藏

-

393 收藏

-

357 收藏

-

158 收藏

-

205 收藏

-

428 收藏

-

265 收藏

-

273 收藏

-

106 收藏

-

187 收藏

-

454 收藏

-

293 收藏

-

248 收藏

-

- 前端进阶之JavaScript设计模式

- 设计模式是开发人员在软件开发过程中面临一般问题时的解决方案,代表了最佳的实践。本课程的主打内容包括JS常见设计模式以及具体应用场景,打造一站式知识长龙服务,适合有JS基础的同学学习。

- 立即学习 543次学习

-

- GO语言核心编程课程

- 本课程采用真实案例,全面具体可落地,从理论到实践,一步一步将GO核心编程技术、编程思想、底层实现融会贯通,使学习者贴近时代脉搏,做IT互联网时代的弄潮儿。

- 立即学习 516次学习

-

- 简单聊聊mysql8与网络通信

- 如有问题加微信:Le-studyg;在课程中,我们将首先介绍MySQL8的新特性,包括性能优化、安全增强、新数据类型等,帮助学生快速熟悉MySQL8的最新功能。接着,我们将深入解析MySQL的网络通信机制,包括协议、连接管理、数据传输等,让

- 立即学习 500次学习

-

- JavaScript正则表达式基础与实战

- 在任何一门编程语言中,正则表达式,都是一项重要的知识,它提供了高效的字符串匹配与捕获机制,可以极大的简化程序设计。

- 立即学习 487次学习

-

- 从零制作响应式网站—Grid布局

- 本系列教程将展示从零制作一个假想的网络科技公司官网,分为导航,轮播,关于我们,成功案例,服务流程,团队介绍,数据部分,公司动态,底部信息等内容区块。网站整体采用CSSGrid布局,支持响应式,有流畅过渡和展现动画。

- 立即学习 485次学习