中国科学院GAA晶体管研制成功,接近理想开关

时间:2025-03-28 11:58:54 239浏览 收藏

中国科学院微电子所研制出新型GAA晶体管,其亚阈值摆幅达到创纪录的60.3 mV/dec,接近理论极限,性能提升超过20%。该团队采用低温臭氧准原子层蚀刻(qALE)技术,精准去除纳米片沟道表面残留的Ge原子,有效降低了界面态密度,解决了当前堆叠式GAA晶体管面临的沟道界面态密度大、难以达到理想开关特性的难题。这项突破性成果为高性能GAA晶体管的低成本制备提供了新途径,相关论文已发表在IEEE Electron Device Letters期刊上并被选为封面论文。 该技术有望推动集成电路技术进一步发展,助力中国在芯片领域取得领先地位。

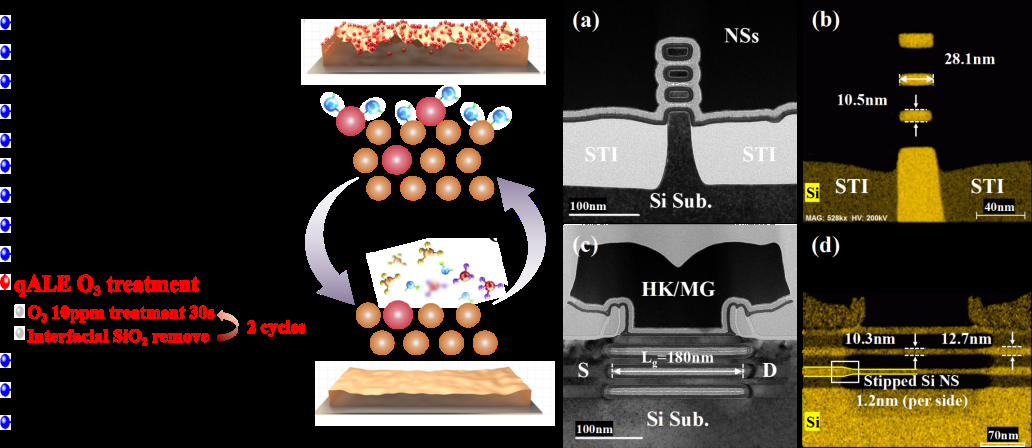

堆叠式全环绕栅极(GAA)晶体管,凭借其优异的栅极控制能力、驱动性能和电路设计灵活性,有望成为FinFET之后的集成电路主流晶体管结构。三星、台积电和英特尔等行业巨头已在3纳米及以下工艺节点开始或计划大规模采用GAA晶体管。然而,当前堆叠式纳米片GAA器件面临沟道界面态密度较大的挑战,难以达到理想的亚阈值开关特性。其主要原因是GeSi/Si超晶格叠层在材料界面易受工艺热预算影响,导致Ge原子扩散和重新分布,从而在纳米片沟道表面残留微量Ge原子,形成额外界面缺陷,降低载流子导电性能。

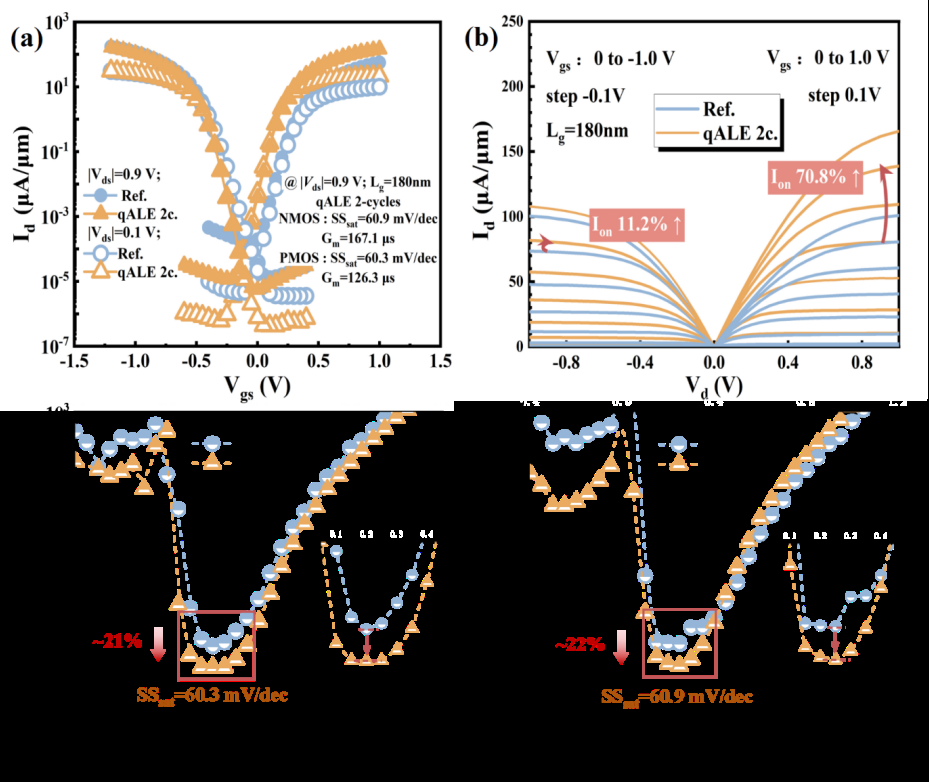

为克服这一难题,中国科学院微电子所集成电路先导工艺研发团队开发了一种低温臭氧准原子层蚀刻(qALE)技术,该技术与GAA晶体管纳米片沟道释放工艺完全兼容。通过极薄臭氧的自限制氧化和腐蚀反应,qALE技术精准去除纳米片沟道表面残留的Ge原子,同时避免损伤内层硅沟道。实验结果表明,经过低温qALE处理后,CMOS器件的界面态密度降低了两个数量级,晶体管亚阈值摆幅优化至60.3 mV/dec,接近器件热力学理论极限(60 mV/dec),漏电流降低了66.7%。此外,由于沟道表面电荷引起的载流子散射减少,晶体管开态电流提升超过20%。这项研究为高效低成本制备高性能堆叠式纳米片GAA器件提供了新的技术途径。

相关研究成果论文“基于O3的准原子层蚀刻技术在全环绕栅极纳米片CMOS器件中实现创纪录的60.3 mV/dec亚阈值摆幅和>20%性能提升”(doi:10.1109/LED.2024.3524259)已发表在IEEE Electron Device Letters期刊上,并被选为封面论文(图3)。微电子所蒋任婕和桑冠荞为论文第一作者,张青竹研究员和殷华湘研究员为共同通讯作者。该研究得到了中国科学院战略性先导专项(A类)和国家自然科学基金的支持。

图1:低温臭氧准原子层蚀刻(qALE)技术与GAA晶体管沟道形貌

图2:沟道qALE处理后的GAA CMOS晶体管电学特性

图3:论文入选IEEE EDL期刊封面

以上就是《中国科学院GAA晶体管研制成功,接近理想开关》的详细内容,更多关于性能提升,GAA晶体管,低温臭氧qALE,亚阈值摆幅,界面态密度的资料请关注golang学习网公众号!

-

501 收藏

-

501 收藏

-

501 收藏

-

501 收藏

-

501 收藏

-

493 收藏

-

147 收藏

-

106 收藏

-

382 收藏

-

443 收藏

-

290 收藏

-

179 收藏

-

292 收藏

-

328 收藏

-

241 收藏

-

122 收藏

-

306 收藏

-

- 前端进阶之JavaScript设计模式

- 设计模式是开发人员在软件开发过程中面临一般问题时的解决方案,代表了最佳的实践。本课程的主打内容包括JS常见设计模式以及具体应用场景,打造一站式知识长龙服务,适合有JS基础的同学学习。

- 立即学习 543次学习

-

- GO语言核心编程课程

- 本课程采用真实案例,全面具体可落地,从理论到实践,一步一步将GO核心编程技术、编程思想、底层实现融会贯通,使学习者贴近时代脉搏,做IT互联网时代的弄潮儿。

- 立即学习 516次学习

-

- 简单聊聊mysql8与网络通信

- 如有问题加微信:Le-studyg;在课程中,我们将首先介绍MySQL8的新特性,包括性能优化、安全增强、新数据类型等,帮助学生快速熟悉MySQL8的最新功能。接着,我们将深入解析MySQL的网络通信机制,包括协议、连接管理、数据传输等,让

- 立即学习 500次学习

-

- JavaScript正则表达式基础与实战

- 在任何一门编程语言中,正则表达式,都是一项重要的知识,它提供了高效的字符串匹配与捕获机制,可以极大的简化程序设计。

- 立即学习 487次学习

-

- 从零制作响应式网站—Grid布局

- 本系列教程将展示从零制作一个假想的网络科技公司官网,分为导航,轮播,关于我们,成功案例,服务流程,团队介绍,数据部分,公司动态,底部信息等内容区块。网站整体采用CSSGrid布局,支持响应式,有流畅过渡和展现动画。

- 立即学习 485次学习