CadenceUCIeIP在三星5nm车规工艺上成功流片

时间:2025-04-15 10:20:21 256浏览 收藏

一分耕耘,一分收获!既然打开了这篇文章《Cadence UCIe IP 在 Samsung Foundry 的 5nm 汽车工艺上实现流片成功》,就坚持看下去吧!文中内容包含等等知识点...希望你能在阅读本文后,能真真实实学到知识或者帮你解决心中的疑惑,也欢迎大佬或者新人朋友们多留言评论,多给建议!谢谢!

Cadence 基于UCIe™标准的封装IP在三星5nm汽车工艺上成功完成首次流片,标志着Cadence持续致力于提供满足新一代汽车电子和高性能计算应用严格要求的高性能车规级IP解决方案。

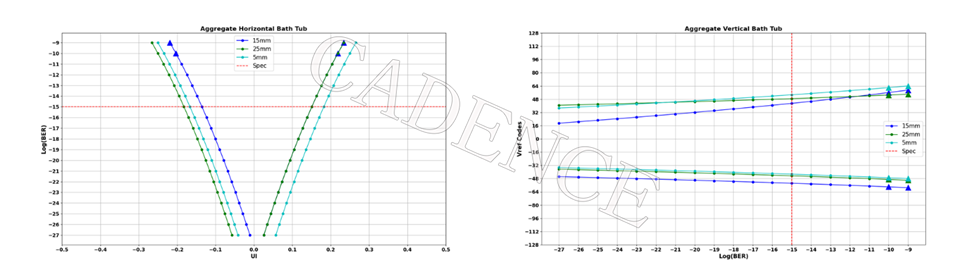

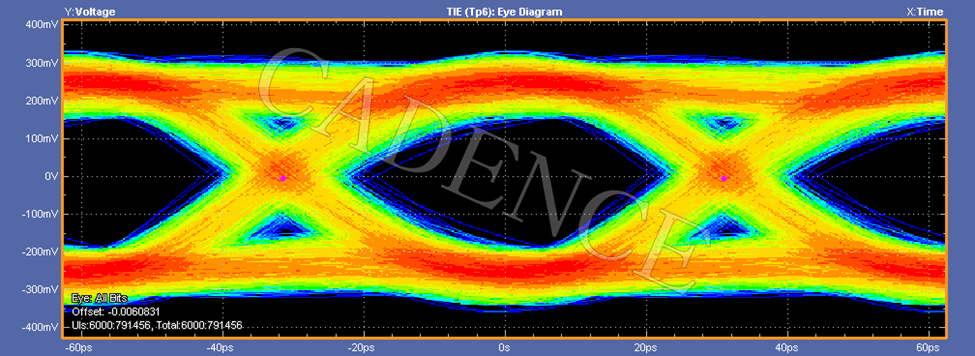

Cadence的UCIe IP在最高16GT/s速率及所有支持的低速率下均实现全功能运行,眼图质量和误码率(BER)远超规范要求。此性能验证了设计的稳健性和可靠性,可轻松集成到对能效和可靠性要求极高的汽车电子和数据中心应用中。

图1:16GT/s速度下,所有信道长度均展现卓越性能,大幅超出UCIe规范要求。

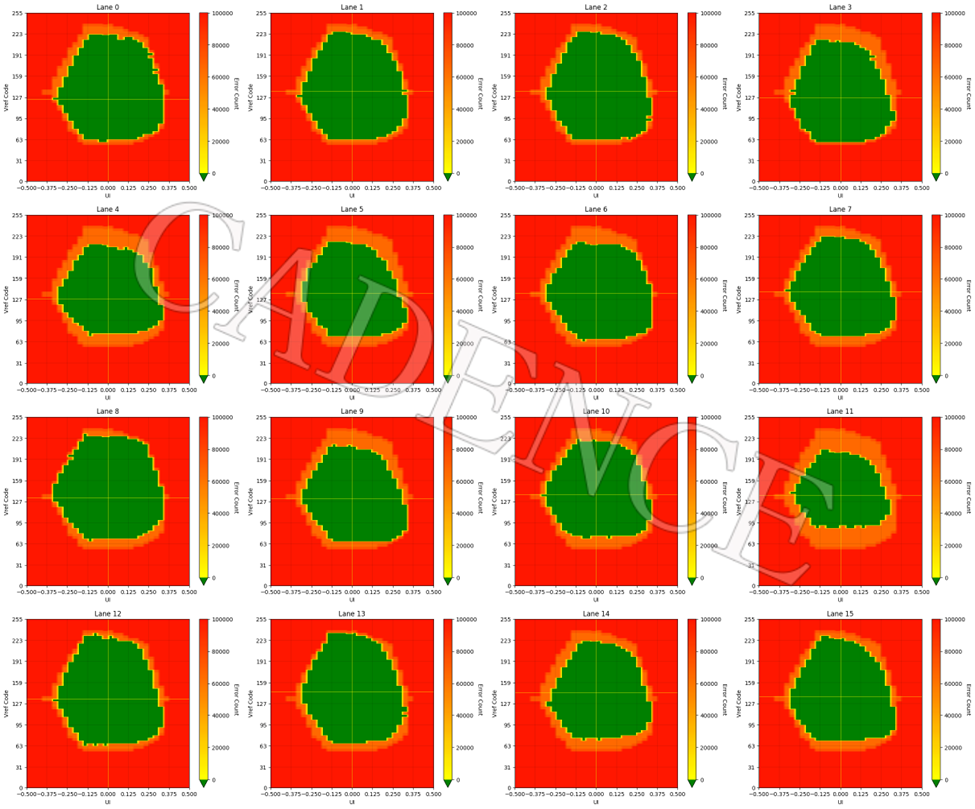

图1的浴盆曲线显示,相位插值器和Vref在1e-15规范要求下(红色虚线)的眼图性能,在短、中、长芯片间距下均表现出优异的接收器性能。图2展示了使用PRBS检查器测量的接收器眼图,PRBS模式在UCIe信道上以最大速度持续传输。硬件成功启动和训练流程确保所有通道均呈现完全打开的眼图。

图2:16GT/s下PRBS模式,所有通道显示良好的接收眼图。

该PHY支持16Tx和16Rx标准封装的全双工通信互联,最大距离达25mm。经过各种距离和布线方法的广泛测试验证了其性能。该PHY基于三星5nm汽车工艺实现,符合UCIe规范和严格的汽车行业要求。在对HPC/AI/ML应用至关重要的多芯片设计中,PHY可在芯片间提供低功耗、低延迟的无缝通信,从而支持高性能计算(HPC)应用。

图3:Cadence是UCIe核心成员之一,积极参与制定包括汽车领域在内的技术规范。

为补充PHY,Cadence提供各种配置的UCIe控制器产品组合。从原始流接口到完整的PCIe协议,以及轻量级、高效的AXI、CXS.B和CHI-C2C接口,Cadence均提供支持。我们的控制器产品组合具有多种配置,包括UCIe-CXS和UCIe-AXI,并已获得SGS的ASIL-B车规认证。交付前,控制器和PHY可在IP子系统中无缝合并,并在各级进行广泛验证,提供简便的集成体验,使客户能够专注于SoC差异化设计。

Cadence与三星晶圆代工持续合作,为双方共同客户提供业界领先的IP解决方案,助力加速创新,将新一代汽车和高性能计算系统推向市场。

图4:示波器显示16GT/s下的UCIe Tx眼图。

Cadence将继续突破互联和系统性能的界限,欲了解更多Cadence UCIe产品信息,请点击此处。

以上就是本文的全部内容了,是否有顺利帮助你解决问题?若是能给你带来学习上的帮助,请大家多多支持golang学习网!更多关于科技周边的相关知识,也可关注golang学习网公众号。

-

501 收藏

-

501 收藏

-

501 收藏

-

501 收藏

-

501 收藏

-

155 收藏

-

385 收藏

-

484 收藏

-

457 收藏

-

176 收藏

-

175 收藏

-

355 收藏

-

458 收藏

-

402 收藏

-

165 收藏

-

335 收藏

-

389 收藏

-

- 前端进阶之JavaScript设计模式

- 设计模式是开发人员在软件开发过程中面临一般问题时的解决方案,代表了最佳的实践。本课程的主打内容包括JS常见设计模式以及具体应用场景,打造一站式知识长龙服务,适合有JS基础的同学学习。

- 立即学习 543次学习

-

- GO语言核心编程课程

- 本课程采用真实案例,全面具体可落地,从理论到实践,一步一步将GO核心编程技术、编程思想、底层实现融会贯通,使学习者贴近时代脉搏,做IT互联网时代的弄潮儿。

- 立即学习 516次学习

-

- 简单聊聊mysql8与网络通信

- 如有问题加微信:Le-studyg;在课程中,我们将首先介绍MySQL8的新特性,包括性能优化、安全增强、新数据类型等,帮助学生快速熟悉MySQL8的最新功能。接着,我们将深入解析MySQL的网络通信机制,包括协议、连接管理、数据传输等,让

- 立即学习 500次学习

-

- JavaScript正则表达式基础与实战

- 在任何一门编程语言中,正则表达式,都是一项重要的知识,它提供了高效的字符串匹配与捕获机制,可以极大的简化程序设计。

- 立即学习 487次学习

-

- 从零制作响应式网站—Grid布局

- 本系列教程将展示从零制作一个假想的网络科技公司官网,分为导航,轮播,关于我们,成功案例,服务流程,团队介绍,数据部分,公司动态,底部信息等内容区块。网站整体采用CSSGrid布局,支持响应式,有流畅过渡和展现动画。

- 立即学习 485次学习