AMIBIOS高级设置全解析

时间:2025-09-14 19:00:57 325浏览 收藏

本文深入解析了AMI BIOS高级设置,旨在帮助用户优化电脑性能。文章详细介绍了高级芯片组配置,包括内存时序的精准调节,如频率响应、延迟表现等。针对内存设置,阐述了SPD信息读取与用户自定义模式的选择,并强调了手动设置的风险与注意事项。此外,还涵盖了内存时钟频率、CAS延迟、行预充电时间、RAS脉冲宽度等关键参数的调整方法,以及AGP相关设置,如工作模式、快写功能、孔径大小等。通过本文,用户能够更深入地了解AMI BIOS的各项高级功能,从而实现系统稳定性与性能的最佳平衡。

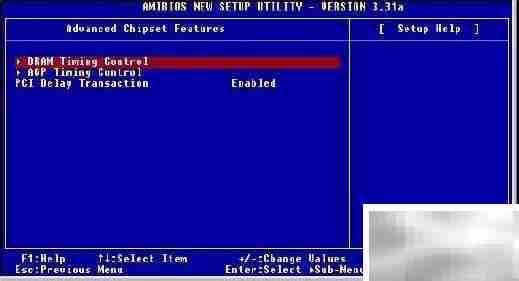

1、深入解析AMI BIOS高级芯片组配置:全面操作指引与设置说明

2、精准调节内存时序,提升频率响应与延迟表现

3、按下回车键进入下级菜单,界面将呈现如下内容。

4、当前计算机系统的实时时钟信息

5、展示当前CPU实际运行的主频数据。

6、内存时钟参数的设定依赖于是否读取内存条上的SPD(串行存在检测)芯片信息。若启用此选项,系统将自动根据SPD中存储的数据配置内存相关参数,包括内存频率、CAS延迟、行预充电时间、RAS脉冲宽度、RAS至CAS延迟以及内存Bank交错模式等。该方式适合大多数普通用户,特别推荐给不熟悉BIOS设置的使用者,可有效避免因手动调整导致的系统不稳定。若选择“用户自定义”模式,则允许用户手动调节上述各项参数,适用于具备一定硬件知识并追求性能极限的进阶用户。但需注意,手动设置存在风险,错误配置可能导致开机失败或系统运行异常。建议在充分理解各参数含义的前提下谨慎操作,以实现系统稳定性与内存性能的最佳平衡。

7、内存时钟频率是决定SDRAM数据传输速率的核心参数。

8、通过此项设置可调整所安装内存的实际工作频率,支持选项包括:200MHz、266MHz、333MHz、400MHz及自动识别模式。关于DDR400内存模块的具体推荐配置,请参考文末附录说明。

9、SDRAM的CAS延迟,即列地址选通有效所需的时间。

10、当SDRAM接收到读取命令后,其响应延迟以时钟周期为单位进行设定,可选值为1.5、2、2.5和3.0个周期。设置为2个周期有助于提高整体性能表现;而设置为3个周期则更有利于增强系统运行的稳定性,用户可根据使用场景灵活选择。

11、行预充电所需的时间,也称为行预充电延迟(tRP)。

12、该选项用于调节行地址选通(RAS)完成前所需的预充电时钟周期数。若预充电时间过短,可能造成内存刷新不完全,进而引发数据错误。此设置仅对同步DRAM生效,可选值为2T或3T,合理配置有助于保障内存稳定运行。

13、RAS脉冲宽度,表示RAS信号持续的有效时间。

14、此设置需依据内存规格调整RAS脉冲宽度对应的时钟周期数。较小的数值可提升DRAM访问速度,提供选项为6T或5T。

15、从行地址选通到列地址选通之间的延迟时间(tRCD)

16、在DRAM完成刷新后,需要分别对行和列进行寻址。本项用于调节从RAS切换到CAS之间的等待周期。较短的延迟可提升内存访问效率。可选设置为3T或2T,数值越低,性能越强。

17、内存Bank交错模式(Bank Interleave),即插槽通道数量配置

18、该设置用于指定SDRAM的工作模式为双通道或四通道。若系统仅安装了16MB SDRAM,建议关闭此功能。可选模式包括:关闭、双通道和四通道。

19、DDR DQS输入延迟,指数据选通信号从发送端传输至接收端的延迟时间。

20、可通过调节DQS延迟来优化数据吞吐效率与系统稳定性,选项包括:Auto、18、08、0E、0F。

21、SDRAM突发长度用于定义一次突发读取操作中连续输出的数据量。当内存接收到初始地址后,会自动预取后续地址的数据,这种机制称为突发模式。要启用该功能,必须设定突发长度,即每次突发传输包含多少个数据单元。该设置使内存内部地址计数器能够正确生成下一个地址,从而加快数据读取速度。突发长度越大,单位时间内传输的数据越多,内存访问效率越高。可选值包括4个四字(4 QW)和8个四字(8 QW),用户可根据系统需求选择最优配置以提升性能。

22、SDRAM 1T指令模式,一种控制内存操作时序的指令方式。

23、该选项用于调整SDRAM控制器的指令执行节奏。启用时,控制器以1T(T代表一个时钟周期)模式运行,响应更快;禁用时则采用2T模式,响应相对缓慢。1T模式在性能上更具优势。用户可在“启用”与“禁用”之间选择,以设定内存控制器的工作节奏,进而影响整体响应效率。

24、高效指令处理,实现快速运算响应

25、此设置用于调控CPU的运行状态。选择“极速”模式可使CPU以最高性能运行,处理数据和指令最为迅速;“快速”模式下运算速度较快;而“正常”模式则降低CPU运行速度,适用于常规办公与日常应用。

26、加速产品从研发阶段向量产落地的进程,全面提升企业运营效率与市场响应能力。

27、任意内存库的读请求均可中断正在进行的突发读取,并允许访问任意列地址。两次读操作之间的最小间隔为一个时钟周期。开启此功能可减少切换延迟,提升系统整体响应速度。提供关闭和开启两种选项供用户选择。

28、AGP时序控制选项,按回车键进入子菜单后,屏幕将显示以下内容。

29、AGP工作模式,即图形加速端口的运行方式

30、为AGP显卡选择合适的运行模式,可选1x、2x、4x或自动识别。只有当显卡本身支持4x模式时才应启用该选项,否则请选择兼容性更好的其他模式。

31、AGP快写功能,显著提升图形数据写入效率。

32、该选项用于开启或关闭AGP快写(Fast Write)功能。启用后,CPU可直接将数据写入显卡显存,无需经过系统内存中转,从而显著提升AGP 4X下的数据传输速率。仅当使用的AGP显卡支持该技术时,才建议开启此功能。

33、支持启用或禁用两种状态切换。

34、AGP孔径大小,直接影响显卡与系统内存间数据交换的带宽与效率。

35、此设置用于设定系统内存中划拨给AGP显卡使用的专用区域大小。所谓“孔径”,是指在PCI内存地址空间内预留的一段专用于图形数据传输的区域。当主时钟周期进入该范围时,数据可直接传输至AGP总线,无需额外地址转换。可选值包括4MB、8MB、16MB、32MB、64MB、128MB和256MB,用户应根据显卡性能及系统负载情况选择合适大小,以优化图形处理性能。

36、AGP主控总线写入时插入一个等待周期的功能控制

37、该设置允许在AGP总线执行写操作时加入一个等待周期,用户可选择启用或禁用,用于微调数据传输时序以适应不同硬件环境。

38、AGP主控总线读取时添加一个等待状态的操作控制

39、在AGP总线读取数据过程中可增加一个等待周期,有助于提升数据传输的稳定性,用户可根据实际情况选择开启或关闭。

40、AGP读取同步功能,确保数据在读取过程中保持一致性与时序准确。

41、此处可设置读同步功能的开关状态,提供开启和关闭两个选项。

42、PCI延迟处理机制,指在PCI总线通信中因外设响应延迟而导致的数据传输停滞现象。

43、芯片组内置32位写入缓存,支持延迟处理周期,能够在ISA总线繁忙时暂存系统与ISA之间的数据,待ISA空闲后再继续传输,从而使PCI总线得以执行其他任务。启用该功能可确保符合PCI 2.1规范要求。该选项提供启用和禁用两种选择,用户可根据系统配置与性能需求进行设定,以优化总线协调能力与整体运行效率。

今天关于《AMIBIOS高级设置全解析》的内容就介绍到这里了,是不是学起来一目了然!想要了解更多关于的内容请关注golang学习网公众号!

-

501 收藏

-

501 收藏

-

501 收藏

-

501 收藏

-

501 收藏

-

262 收藏

-

375 收藏

-

172 收藏

-

367 收藏

-

243 收藏

-

157 收藏

-

221 收藏

-

104 收藏

-

380 收藏

-

467 收藏

-

465 收藏

-

123 收藏

-

- 前端进阶之JavaScript设计模式

- 设计模式是开发人员在软件开发过程中面临一般问题时的解决方案,代表了最佳的实践。本课程的主打内容包括JS常见设计模式以及具体应用场景,打造一站式知识长龙服务,适合有JS基础的同学学习。

- 立即学习 543次学习

-

- GO语言核心编程课程

- 本课程采用真实案例,全面具体可落地,从理论到实践,一步一步将GO核心编程技术、编程思想、底层实现融会贯通,使学习者贴近时代脉搏,做IT互联网时代的弄潮儿。

- 立即学习 516次学习

-

- 简单聊聊mysql8与网络通信

- 如有问题加微信:Le-studyg;在课程中,我们将首先介绍MySQL8的新特性,包括性能优化、安全增强、新数据类型等,帮助学生快速熟悉MySQL8的最新功能。接着,我们将深入解析MySQL的网络通信机制,包括协议、连接管理、数据传输等,让

- 立即学习 500次学习

-

- JavaScript正则表达式基础与实战

- 在任何一门编程语言中,正则表达式,都是一项重要的知识,它提供了高效的字符串匹配与捕获机制,可以极大的简化程序设计。

- 立即学习 487次学习

-

- 从零制作响应式网站—Grid布局

- 本系列教程将展示从零制作一个假想的网络科技公司官网,分为导航,轮播,关于我们,成功案例,服务流程,团队介绍,数据部分,公司动态,底部信息等内容区块。网站整体采用CSSGrid布局,支持响应式,有流畅过渡和展现动画。

- 立即学习 485次学习